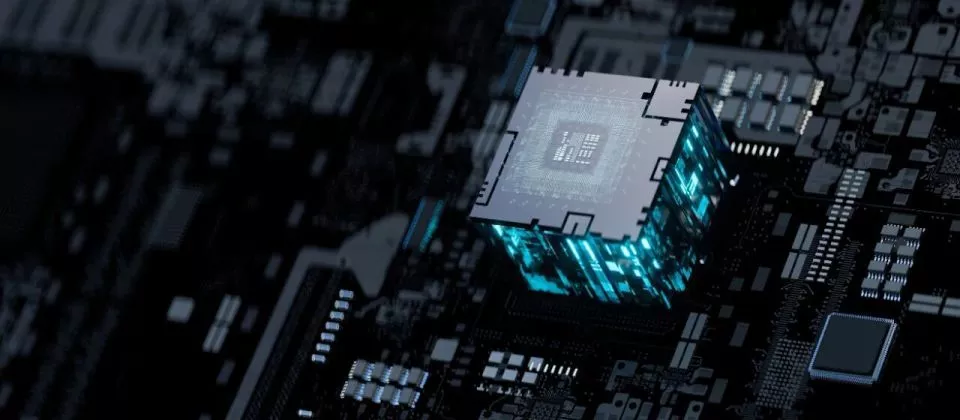

全球首颗!复旦大学创新存储芯片登上Nature顶刊

来源:倍可亲(backchina.com)

芯片良率超过94%。

芯东西10月11日报道,10月8日,复旦大学团队研发的全球首颗二维-硅基混合架构芯片,相关研究成果在国际顶级学术期刊Nature上发表。

该成果将二维超快闪存与成熟互补金属氧化物半导体(CMOS)工艺深度融合,攻克了二维信息器件工程化的关键难题,解决了存储速率的技术难题。

据复旦大学公众号介绍,这颗芯片性能“碾压”目前的Flash闪存技术,首次实现了混合架构的工程化。依托前期完成的研究成果与集成工作,此次打造出的芯片已成功流片。

基于CMOS电路控制二维存储核心的全片测试支持8-bit指令操作,32-bit高速并行操作与随机寻址,良率高达94.34%。

论文题目为《全功能二维-硅基混合架构闪存芯片》。复旦大学集成电路与微纳电子创新学院、集成芯片与系统全国重点实验室研究员刘春森和教授周鹏为论文通讯作者,刘春森研究员和博士生江勇波、沈伯佥、袁晟超、曹振远为论文第一作者。

论文链接:

https://www.nature.com/articles/s41586-025-09621-8

这是时隔半年,继“破晓(PoX)”皮秒闪存器件问世后,复旦大学在二维电子器件工程化领域再获得的一项里程碑式突破。

今年4月,周鹏-刘春森团队于Nature期刊提出“破晓”二维闪存原型器件,实现了400皮秒超高速非易失存储,是迄今最快的半导体电荷存储技术,为打破算力发展困境提供了底层原理。

其团队研发的“长缨(CY-01)”架构将二维超快闪存器件“破晓(PoX)”与成熟硅基CMOS工艺深度融合,研发出一款基于原子级器件到芯片(ATOM2CHIP)技术实现的全功能二维NOR闪存芯片。

▲二维-硅基混合架构闪存芯片光学显微镜照片(图源:复旦大学)

根据论文,二维材料扩展了硅技术器件可扩展能力,并推动器件机制的根本性创新。尽管二维材料集成或2D-CMOS混合集成方面已取得显著进展,但迄今仍缺乏一种能够将器件优势真正转化为实际应用的完整系统。

当前二维半导体尚无法实现与先进硅技术相媲美的逻辑电路性能。因此,将二维电子学与成熟的硅CMOS逻辑电路相结合,是充分发挥二维电子学系统级优势的一条极具前景的路径。

相关前沿研究主要集中在将二维材料与CMOS工艺结合,以提升器件性能。尚缺乏将二维器件概念的优势移植到系统中的核心技术,而开发这样一套系统化流程与设计方法论,需要涵盖从平面集成、三维架构,直至芯片封装的全栈式片上工艺,并需实现跨平台的系统设计。

“存储器是二维电子器件最有可能首个产业化的器件类型。因为它对材料质量和工艺制造没有提出更高要求,而且能够达到的性能指标远超现在的产业化技术,可能会产生一些颠覆性的应用场景。”在存储器领域深耕多年的周鹏认为。

当前,市场中的大部分集成电路芯片均使用CMOS技术制造,产业链较为成熟。团队判断,如果要加快新技术孵化,就要将二维超快闪存器件充分融入CMOS传统半导体产线,而这也能为CMOS技术带来突破。

“从第一个原型晶体管到第一款CPU花了大约24年,而我们通过把先进技术融入工业界现有的CMOS产线,这一原本需要数十年的积累过程被大幅压缩,未来可以进一步加速探索颠覆性应用。”刘春森总结。

团队前期经历了5年的探索试错,在单个器件、集成工艺等多点协同攻关。其第一项集成工作发表于2024年的Nature Electronics,在最理想的原生衬底上实现了二维良率的突破,这为在真实复杂的CMOS衬底上解决问题奠定了基础。

▲二维-硅基混合架构闪存芯片透射电子显微镜照片(图源:复旦大学)

如何将二维材料与CMOS集成又不破坏其性能,是需要攻克的核心难题。

CMOS电路表面有很多元件,而二维半导体材料厚度仅有1-3个原子,如果直接将二维材料铺在CMOS电路上,材料很容易破裂。

“就好比我们从太空看上海,似乎很平坦,但这个城市内部其实有400多米、100多米或者几十米高度不等的建筑。如果铺一张薄膜在城市上方,膜本身就会不平整。”周鹏形象比喻道。

因此,全世界的二维半导体研究者目前只能在极为平整的原生衬底上加工材料。一种解决思路是将CMOS的衬底“磨平”以适应二维材料,但要实现原子级平整并不现实。

周鹏-刘春森团队决定从本身就具有一定柔性的二维材料入手,通过模块化的集成方案,先将二维存储电路与成熟CMOS电路分离制造,再与CMOS控制电路通过高密度单片互连技术(微米尺度通孔)实现完整芯片集成。

这项核心工艺的创新,实现了在原子尺度上让二维材料和CMOS衬底的紧密贴合,最终实现超过94%的芯片良率。

此外,所制备的二维闪存单元支持20纳秒快速操作,且单比特能耗低至0.644皮焦耳。

团队进一步提出了跨平台系统设计方法论,包含二维-CMOS电路协同设计、二维-CMOS跨平台接口设计等,并将这一系统集成框架命名为“长缨(CY-01)架构”。

其跨平台系统设计支持二维NOR闪存芯片的指令驱动型工作模式,具备32位并行处理能力和随机访问功能。

这些特性已通过芯片测试得到验证:测试时钟频率设定为5MHz,编程脉冲则被优化为2.5个时钟周期。

该方法为新兴机制驱动的二维电子器件与成熟CMOS平台之间的兼容性提供了可靠保障。

团队相信,这些系统级成果标志着将二维电子技术的优势拓展至实际应用领域的重要里程碑。

下一步,周鹏-刘春森团队计划建立实验基地,与相关机构合作,建立自主主导的工程化项目,并计划用3-5年时间将项目集成到兆量级水平,期间产生的知识产权和IP可授权给合作企业。

展望未来,该团队期待该技术颠覆传统存储器体系,让通用型存储器取代多级分层存储架构,为人工智能、大数据等前沿领域提供更高速、更低能耗的数据支撑,让二维闪存成为AI时代的标准存储方案。